# Three-Dimensional Passive Circuit Technology For Ultra-Compact MMIC's

Makoto Hirano, Kenjiro Nishikawa, Ichihiko Toyoda, Shinji Aoyama, Suehiro Sugitani, and Kimiyoshi Yamasaki

**Abstract**—A novel passive circuit technology of a three-dimensional (3-D) metal-insulator structure is developed for ultra-compact MMIC's. By combining vertical passive elements, such as a wall-like microwire for shielding or coupling, and a pillar-like via connection with multilayer passive circuits, a 3-D passive circuit structure is formed to implement highly dense and more functional MMIC's.  $O_2/He$  RIE for forming trenches and holes in a thick polyimide insulator, low-current electroplating for forming gold metal sidewalls in the trenches or holes, and ion-milling with a WSiN stopper layer for patterning the gold metal are used to produce such a structure. The complete 3-D structure provides miniature microstrip lines effectively shielded with a vertical metal-wall, a miniature balun with low-loss vertical wall-like microwires, and inverted microstrip lines jointed with pillar-like vias through a thick polyimide layer. This technology stages next-generation ultra-compact MMIC's by producing various functional passive circuits in a very small area.

## I. INTRODUCTION

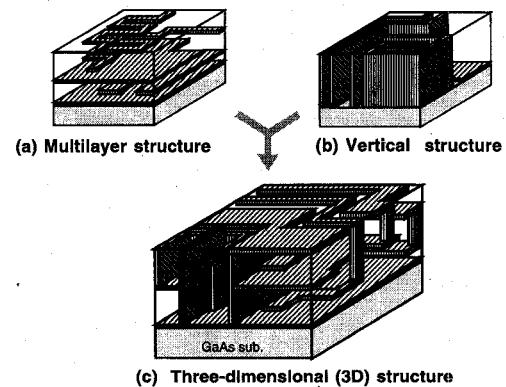

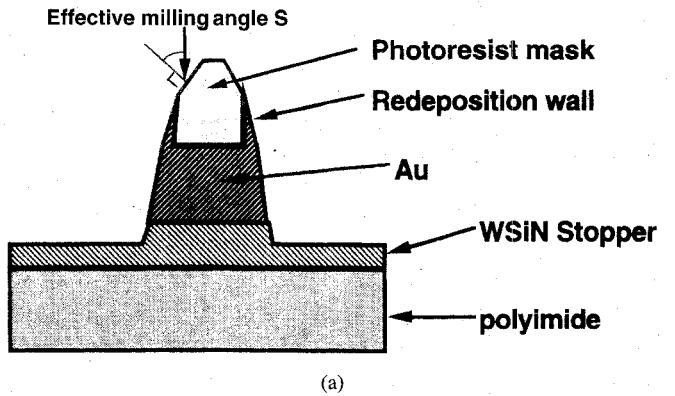

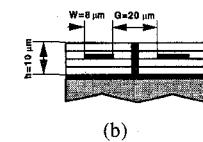

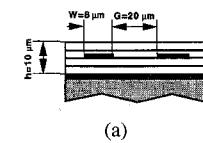

RECENT RAPID improvement in mobile communication has increased demand for highly dense and more functional MMIC's. A multilayer passive circuit with polyimide insulator is one useful approach for such MMIC's [1]–[3]. As shown in Fig. 1(a), two different passive circuits can be formed in the same area with a shield ground plane in the middle metal layer, and moreover, two or more different signal lines can be coupled throughout a window formed in the shield plane. Therefore, by using this technology, miniature dividers, couplers, mixers or many other functional passive circuits have been designed.

On the other hand, vertical microwire technology [4], [5] is another effective device for shrinking the size of MMIC's. As shown in Fig. 1(b), inductors and transmission lines can be miniaturized by a vertical wall-like microwire structure. About one-third to one-fourth miniaturized inductors or transmission lines have been obtained by this technology. If we can combine these two technologies, and add some more advanced features, denser and more highly functional MMIC's will be implemented.

Manuscript received February 28, 1995; revised July 10, 1995.

M. Hirano, S. Aoyama, S. Sugitani, and K. Yamasaki are with the NTT LSI Laboratories, 3-1, Morinosato Wakamiya, Atsugi-shi, Kanagawa Pre., 243-01, Japan.

K. Nishikawa is with the NTT Wireless Systems Laboratories, 3-1, Morinosato Wakamiya, Atsugi-shi, Kanagawa Pre., 243-01, Japan.

I. Toyoda is with the NTT Group Strategy Planning Department, 3-1, Morinosato Wakamiya, Atsugi-shi, Kanagawa Pre., 243-01, Japan.

IEEE Log Number 9415472.

Fig. 1. The structure of compact MMIC's.

In this paper, a novel passive circuit technology for more compact and functional MMIC's is proposed. For staging such next-generation MMIC's, a vertical passive structure and multilayer one are combined in completely three-dimensionalized (3-D) passive structure. As a result, circuit designers can take advantage of smaller chip area and get higher performance and greater design flexibility of MMIC's.

## II. A STRUCTURE

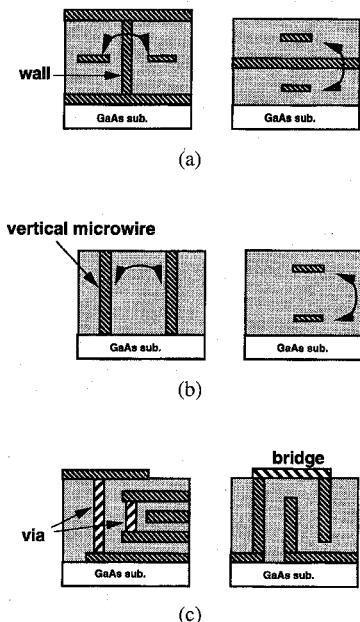

The most desirable structure to advance passive functions of MMIC's is a completely three-dimensional one, which consists of vertical metal structure and multilayer metal-insulator structure, both buried in a thick insulator. In such a structure, many vertical passive elements can be utilized to design MMIC's; a vertical shield wall, a miniature inductor, a miniature transmission line, a vertical coupler and a pillar-like via connection through a thick insulator layer. In addition, all these elements can be put together with a horizontal multi-metal layer, as shown in Fig. 1(c). Fig. 2 shows some examples of combining vertical elements and horizontal elements to make three basic 3-D passive components: a 3-D shield ground plane, coupled signal lines, and 3-D interconnections. By employing these basic 3-D components, a variety of passive functional circuits, such as divider, phase shifter, filter and so forth, can be formed to minimize the chip area and achieve greatly improved performance of MMIC's.

## III. FABRICATION

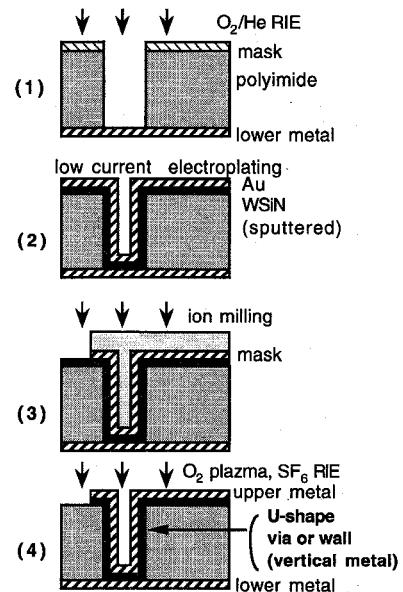

In order to achieve a 3-D passive circuit structure, a new fabrication technology was developed. We call it folded metal

Fig. 2. Three basic effects in 3-D structure. (a) Shielding, (b) coupling, and (c) interconnecting.

interconnection technology with thick insulator (FMIT). In this technology, a *U*-shaped microwire [4], as an essential vertical element, is buried in a thick insulator of multi-metal-insulator-layer structure. The main flow of the fabrication process is shown in Fig. 3.

The process has three key features; First, via-holes and trenches are formed in a 10- $\mu\text{m}$ -thick polyimide insulator layer by RIE. Second, a metal side-wall is formed along the surface of the formed holes and trenches. Finally, the gold grown on the polyimide surface is patterned. The detailed fabrication methods and conditions are as follows.

#### A. $\text{O}_2/\text{He}$ RIE for Polyimide Etching

To form via-holes and trenches in the thick polyimide insulator layer,  $\text{O}_2/\text{He}$  RIE was used. To prevent large side-etching of polyimide, RIE was performed at low pressure, 30 mtorr. In etching for polyimide with thickness over 2  $\mu\text{m}$ , some residue is produced on the bottom surface of the holes and the trenches by using  $\text{O}_2$  RIE without He. To eliminate this residue, a mixture of  $\text{O}_2$  and He was used in RIE. The cleaning effect of the bottom surface by adding He to  $\text{O}_2$  RIE is shown in Fig. 4. In comparison with the bottom surface, formed by only  $\text{O}_2$  RIE, that formed by the mixture gas RIE was cleaner. This cleaning effect is caused by the sputtering effect of He ions. Employing the etching condition of 30 mtorr gas pressure with a 2:1 combination of  $\text{O}_2$  and He at 0.2 W/cm<sup>2</sup> RF power density, vertical holes and trenches were successfully formed without both large side-etching and etching residue.

#### B. Low-Current Electroplating for Gold Metal Sidewall

To form the metal sidewall along the whole surface of the formed holes and trenches in the polyimide, low-current gold

Fig. 3. Process flow of buried vertical *U*-shaped vias or walls.

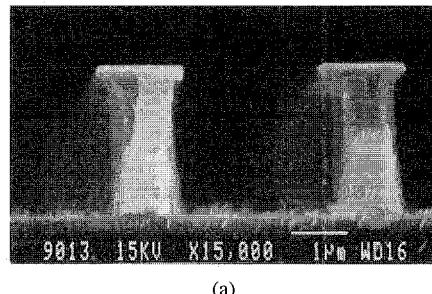

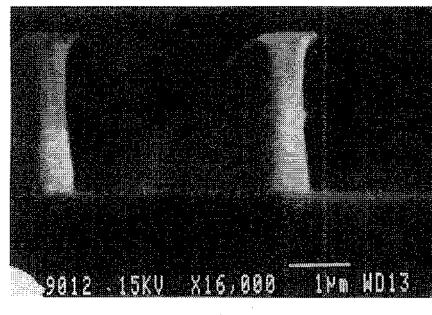

9013 15KV X15,000 1 $\mu\text{m}$  WD16 (a)

9012 15KV X15,000 1 $\mu\text{m}$  WD13 (b)

Fig. 4. SEM images of trenches formed in polyimide. (a) Trenches in a polyimide formed by  $\text{O}_2$  RIE, and (b) trenches in a polyimide formed by  $\text{O}_2/\text{He}$  RIE.

electroplating was applied. By lowering the current density for plating, conformability and uniformity of a plated metal are improved [6].

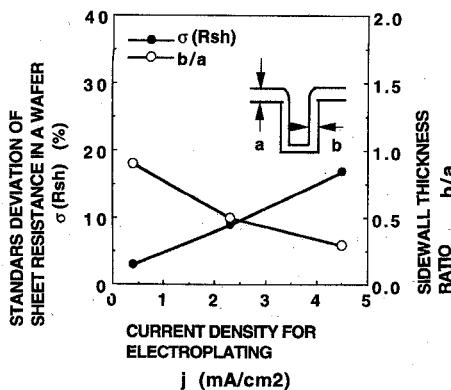

Fig. 5 shows the relation of plating current density versus conformability and uniformity of gold metal. As can be seen in this figure, the relative thickness of the sidewall in a trench and a standard deviation of sheet resistance of the plated gold in a wafer were both increased by lowering the current density, i.e., the plating rate of electroplating.

The crystal structure, with better microscopic uniformity, of the gold plated on the 50-nm-thick gold layer made by

Fig. 5. Conformability of gold metal plated in trenches.

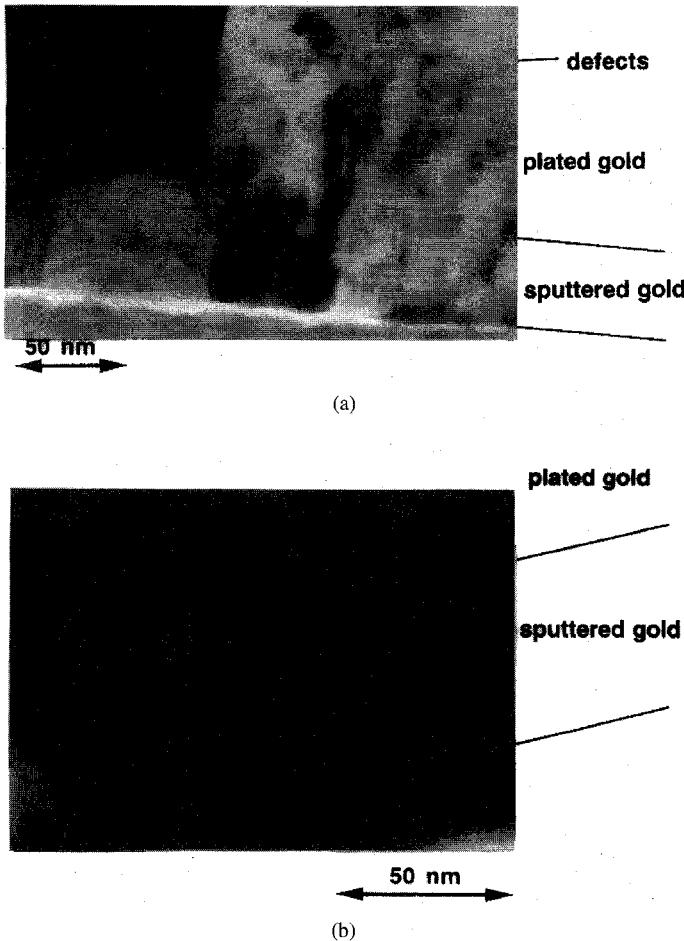

Fig. 6. TEM images of plated gold metal. (a) Gold metal plated by high current density, 3 mA/cm<sup>2</sup>, and (b) gold metal plated by low current density, 0.2 mA/cm<sup>2</sup>.

sputtering deposition was also studied by TEM. Fig. 6(a) shows the grain size and defects in the metal plated by a large current density, 3 mA/cm<sup>2</sup>, and Fig. 6(b) shows those in the metal plated by a small current density, 0.2 mA/cm<sup>2</sup>. Larger grain size and less defects were obtained with the lower current density. The crystal structure obtained with the low current density will take advantage to achieve long lifetime of interconnection microwires by preventing

Fig. 7. Patterned gold metal by ion-milling. (a) Schematic view of Au patterning by ion-milling. (b) SEM image of formed pattern (using a mask photoresist with large thickness), and (c) SEM image of formed pattern (using a mask photoresist with optimized thickness).

electromigration. By using low-current plating conditions, with current density of 0.2 mA/cm<sup>2</sup>, thick gold sidewalls as *U*-shaped vias and vertical microwires were successfully formed.

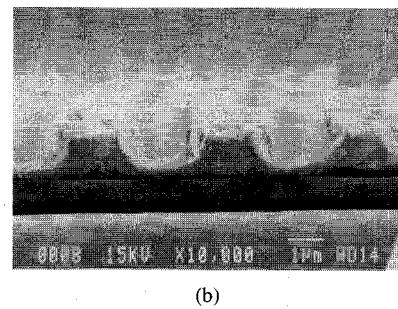

### C. Ion-Milling with WSiN Metal Stopper

To pattern gold grown on the whole surface, including holes and trenches, ion-milling is used with WSiN metal as a stopper. The stopper metal protects the lower polyimide from ion-milling and also from etching when the photoresist as a milling-mask is removed by O<sub>2</sub> plasma. The WSiN layer with thickness of 200–400 nm beneath the gold was useful for patterning a 1-μm-thick gold layer in the 3-D structure.

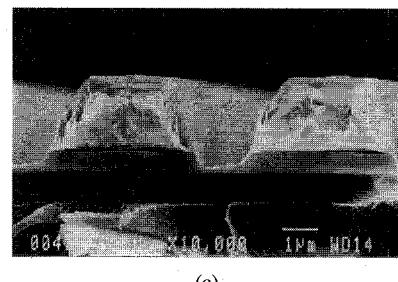

The thickness of the photoresist mask for ion-milling is another key factor to get fine patterns of the gold metal. To prevent redeposition of gold onto the sidewall of the photoresist mask, which often produces electrical short error between upper and lower interconnections, the photoresist

Fig. 8. Fabricated vertical metal structures. (The polyimide has been removed to reveal the metal structure.) (a) Pillar-like vias (10 micron height), and (b) wall-like microwires (10 micron height).

mask should be designed to become thin and tapered at the pattern edges at the end of ion-milling. The milling rate of the photoresist is larger at the pattern edge, i.e., the shoulder of the photoresist, than at the pattern center (shown in Fig. 7(a)) because of the milling rate dependency on the Ar incident angle. Therefore, the optimum thickness of photoresist mask can be designed by the following equation

$$T = t X dT' / \cos S$$

where,  $T$  is thickness of the photoresist,  $t$  is etching time including over-etching time for the gold metal,  $dT'$  is the maximum etching rate of the photoresist for an angled ion-beam,  $S$  is the milling angle for maximum etching rate.

A schematic of the cross section of the mask and the gold metal in the milling process and SEM images of gold patterns fabricated by two photoresist masks with different thickness are shown in Fig. 7(a)–(c). As shown in the Fig. 7(c), the fine gold patterns were formed without redeposition-walls by optimizing the thickness of the photoresist.

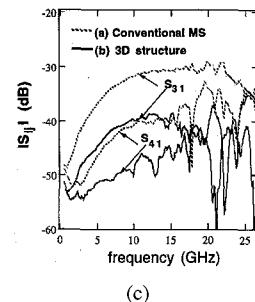

The 3-D passive structure with thickness of 10  $\mu\text{m}$ , fabricated by using all the above-mentioned techniques is shown in Fig. 8(a) and (b). In the figures, the polyimide insulator was almost removed by RIE for SEM observation. The 10- $\mu\text{m}$ -height pillar-like via and metal wall were successfully fabricated. These can be combined with, for example, a multilayer of five 1.4- $\mu\text{m}$ -thick metal layers and four 2.5- $\mu\text{m}$ -thick insulator layers. In such a combined structure, the pillar-like via connections in the height range of 2.5–10  $\mu\text{m}$  have been successfully fabricated with 100% yield in a 3-inch-diameter wafer. Even by only the combination of this vertical structure and the multilayer one, many varieties of miniature passive circuits can be formed on an IC chip as described in the following section.

Fig. 9. Shielding effect of a vertical metal wall for microstrip (MS) lines. (a) Conventional MS (multilayer structure), (b) MS with shield wall (3-D structure), and (c) high frequency characteristics.

#### IV. CIRCUIT APPLICATIONS

Basic effects of 3-D structure have been confirmed as follows.

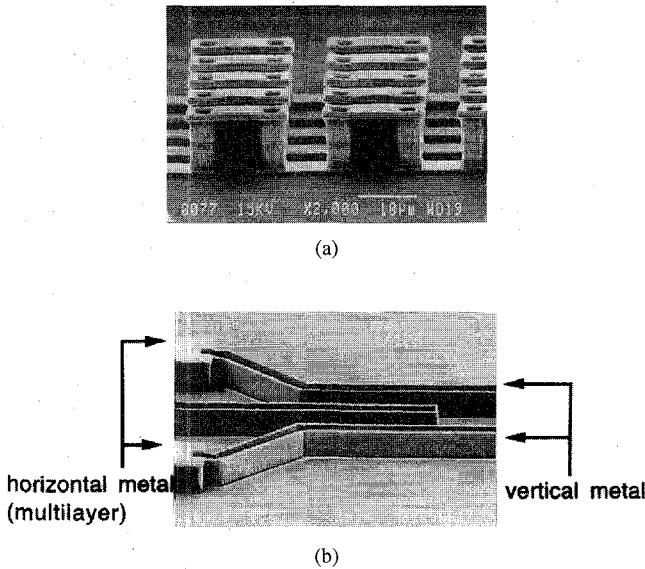

##### A. Shield Effect with Vertical Structure

Fig. 9 shows one example of shielding effect with a vertical metal wall.

The isolation characteristics were compared for two structures; one with only two microstrip (MS) signal lines of multilayer structure being put in separation (Fig. 9(a)), and the other being shielded with a vertical metal wall buried in the thick polyimide (Fig. 9(b)). As shown in Fig. 9(c), the lines can be shielded effectively employing the vertical metal wall. By using the shield effect with a vertical wall or a horizontal plane in the 3-D structure, thin film microstrip (TFMS) lines can offer a significantly reduced occupied area providing strongly isolated crossover.

##### B. Miniature But Low-Loss Characteristics of the Vertical Wall-Like Microwires

Another 3-D passive circuit as an example of using miniature but low-loss vertical microwires, a one-third or less miniaturized wideband balun, has also been successfully operated [7]. A balun with  $1.5 \pm 1 \text{ dB}$  insertion loss over 10–30 GHz and 2 dB and 5 degrees of amplitude and phase balances over 5–35 GHz have been obtained with the intrinsic area of only  $450 \mu\text{m} \times 800 \mu\text{m}$ . The detailed characteristics was described in [7]. By using the coupling effect with vertical or horizontal metals, many other functional passive circuits like dividers, filters and mixers can be fabricated in a small area.

### C. Vertical Pillar-Like Vias Through Thick Polyimide Insulator

Vertical connection by pillar like vias can provide short signal delay and miniaturized connection even through a very thick insulator. An inverted microstrip line (IMSL) with a thick insulator [8] has been successfully formed by this technology, which is useful not only for 3-D MMIC's but also for ultra-high-speed digital IC's.

The 3-D structure can also be used for many other passive elements such as low loss vertical inductors [4], miniature vertical co-planer transmission-lines [5], a multilayer coupler [2], [3] and microstrip lines shielded with a middle layer ground plane [2], [3]. The high-frequency characteristics of these 3-D elements have already been confirmed [2]–[5].

### V. CONCLUSION

Three-dimensional (3-D) passive circuits were successfully fabricated in 10- $\mu\text{m}$ -thick polyimide insulator. A new fabrication technology, folded metal interconnection technology with thick insulator (FMIT), was developed to achieve the 3-D structure. By using this technology, vertical *U*-shape metal walls and vias were buried in the polyimide, which also contained horizontal metal layers. The structure provided miniature microstrip (MS) lines effectively shielded with a vertical wall, and a miniature balun consisted of low-loss vertical microwires. This technology could also provide inverted microstrip lines (IMSL) with a polyimide layer of over 10-mm-thickness. Because 3-D technology can achieve a variety of highly miniaturized and functional passive circuits, it enables us to implement ultra-compact MMIC's.

### ACKNOWLEDGMENT

The authors wish to thank K. Hirata and M. Aikawa for their valuable advice and encouragement. Thanks are also due to T. Tokumitsu for his fruitful suggestions on designing three-dimensional MMIC's and M. Satoh for her helpful assistance in circuit fabrication.

### REFERENCES

- [1] M. W. Green, G. J. Green, R. G. Arnold, J. A. Jenkins, and R. H. Jansen, "Miniature multilayer spiral inductors for GaAs MMIC's," in *IEEE GaAs IC Symp.*, 1989, pp. 303–306.

- [2] T. Tokumitsu, T. Hiraoka, H. Nakamoto, and T. Takenaka, "Multilayer MMIC using a 3  $\mu\text{m}$   $\times$  3-layer dielectric film structure," in *1990 IEEE MTT-S Dig.*, S-5, June 1990, pp. 831–834.

- [3] I. Toyoda, T. Hirota, T. Hiraoka, and T. Tokumitsu, "Multilayer MMIC branch-line coupler and broad-side coupler," in *IEEE 1992, MMWMC Dig.*, June 1992, pp. 79–82.

- [4] M. Hirano, Y. Imai, and K. Asai, "1/4 Miniaturized passive elements for GaAs MMIC's," in *IEEE GaAs IC Symp.*, 1991, pp. 34–40.

- [5] M. Hirano, I. Toyoda, M. Tokumitsu, and K. Asai, "Folded *U*-shaped microwire technology for GaAs IC interconnections," in *IEEE GaAs IC Symp.*, 1992, pp. 177–180.

- [6] M. Hirano, A. Aoyama, and K. Yamasaki, "Submicrometer gold interconnect wiring by sidewall electroplating technology," *Jpn. J. Appl. Phys.*, vol. 33, pp. L553–L555, Apr. 1994.

- [7] I. Toyoda, M. Hirano, and T. Tokumitsu, "An ultra-wide band miniature Balun for 3-dimensional MMIC's," *APMC*, vol. 22, no. 2, pp. 511–514, Dec. 1994.

- [8] S. Yamaguchi, Y. Imai, T. Shibata, T. Otsuji, M. Hirano, and E. Sano, "An inverted microstrip line IC structure for ultra-high-speed applications," in *IEEE MTT-S Dig.*, May 1995, pp. 1643–1646.

**Makoto Hirano** was born in Tokyo, Japan, in 1952. He received the B.E., M.S., and D.E. degrees from Waseda University, Tokyo, Japan, in 1977, 1979, and 1992, respectively.

From 1979 to 1983, he worked in the Musasino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation (NTT), Tokyo, Japan, where he was engaged in research and development of magnetic bubble devices. In 1983, he joined the Atsugi Electrical Communication Laboratory (now NTT LSI Laboratories) Kanagawa, Japan. He is presently a member of the GaAs MESFET Technology Group, with research interest in advanced GaAs MMIC technology.

Dr. Hirano is a member of the Japan Society of Applied Physics and the IEEE. He received Japan Microwave Prize on the research of three-dimensional MMIC technology, at Asia Pacific Microwave Conference in 1995.

**Kenjiro Nishikawa**, for a photograph and biography, see this issue p. 2816.

**Ichihiko Toyoda** was born in Osaka, Japan, 1962. He received the B.E., M.E., and D.E. degrees in communication engineering from Osaka University, Osaka, Japan, in 1985, 1987, and 1990, respectively.

In 1990 joined NTT Radio Communications Systems Laboratories, Kanagawa, Japan. In 1994 he moved to NTT Electronics Technology Corporation, Kanagawa, Japan on leave from NTT. His current interests are a three-dimensional and uniplanar MMIC's, and their applications based on electromagnetic analysis.

Dr. Toyoda was granted the 1993 Young Engineer Award by the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan. He is also a recipient of the Japan Microwave Prize granted at 1994 Asia-Pacific Microwave Conference held in Tokyo, Japan, in 1994. He is a member of the IEICE.

**Shinji Aoyama** was born in Saitama, Japan, in 1949.

From 1968 to 1983, he worked in the Musasino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation (NTT), Tokyo, Japan, where he was engaged in fabrication process engineering of Si LSIs. In 1983, he joined the Atsugi Electrical Communication Laboratory (now NTT LSI Laboratories), Kanagawa, Japan. He is presently a Senior Research Engineer, and is engaging in photolithography technology of GaAs IC's.

Mr. Aoyama is a member of the Japan Society of Applied Physics.

**Suehiro Sugitani** was born in Kumamoto, Japan, on June 4, 1960. He received the B.E. and M.E. degrees in electronics engineering from Kyushu University, Fukuoka, Japan, in 1983 and 1985, respectively. In 1985, he joined the NTT Atsugi Electrical Communication Laboratory, Kanagawa, Japan. Since joining NTT, he has been engaged in research and development of process technology for high-speed GaAs MESFETs. He is now a Senior Research Engineer with NTT LSI Laboratories, Kanagawa, Japan.

Mr. Sugitani is a member of the Japan Society of Applied Physics and the Institute of Electronics, Information and Communication Engineers of Japan.

**Kimiyoshi Yamasaki** was born in Ehime Prefecture, Japan, in 1952. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1975, 1977, and 1980, respectively.

In 1980, he joined the NTT Musashino Electrical Communication Laboratories, Tokyo, Japan. Since then, he has been engaged in research on GaAs high-speed device and process technologies and ATM switching system with optical interconnection. In 1988, he spent a year at Cornell University, Ithaca, NY, as a Visiting Scientist, where he worked on ballistic electron devices. He is currently a Senior Research Engineer, Supervisor, at the NTT LSI Laboratories in Atsugi, Japan, where he is responsible for the research and development of advanced GaAs IC technology.

Dr. Yamasaki is a member of the Institute of Electronics, Information and Communication Engineers of Japan and the Japan Society of Applied Physics.